**번역본뉴스입니다. 오역이 있을수 있습니다.

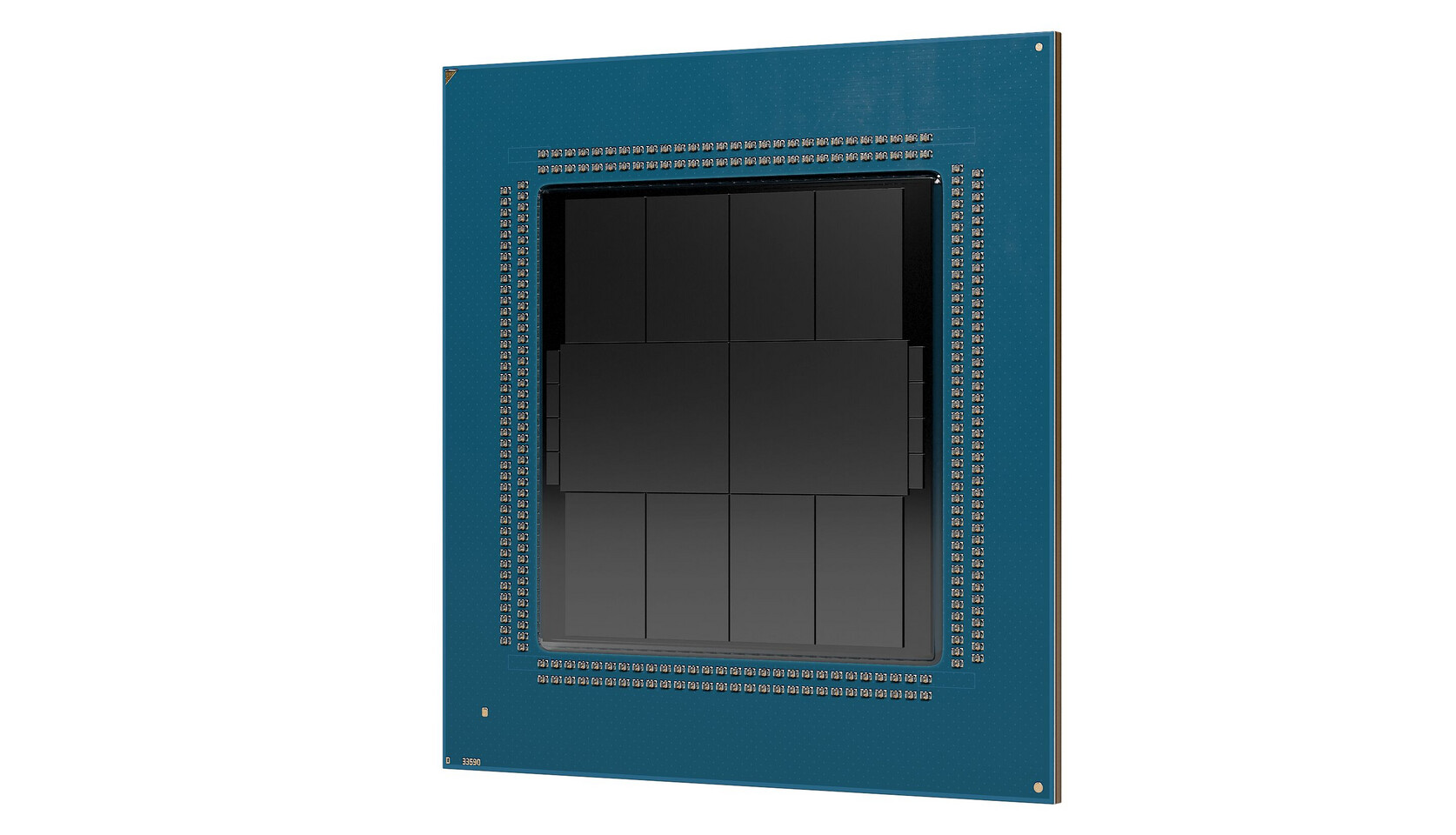

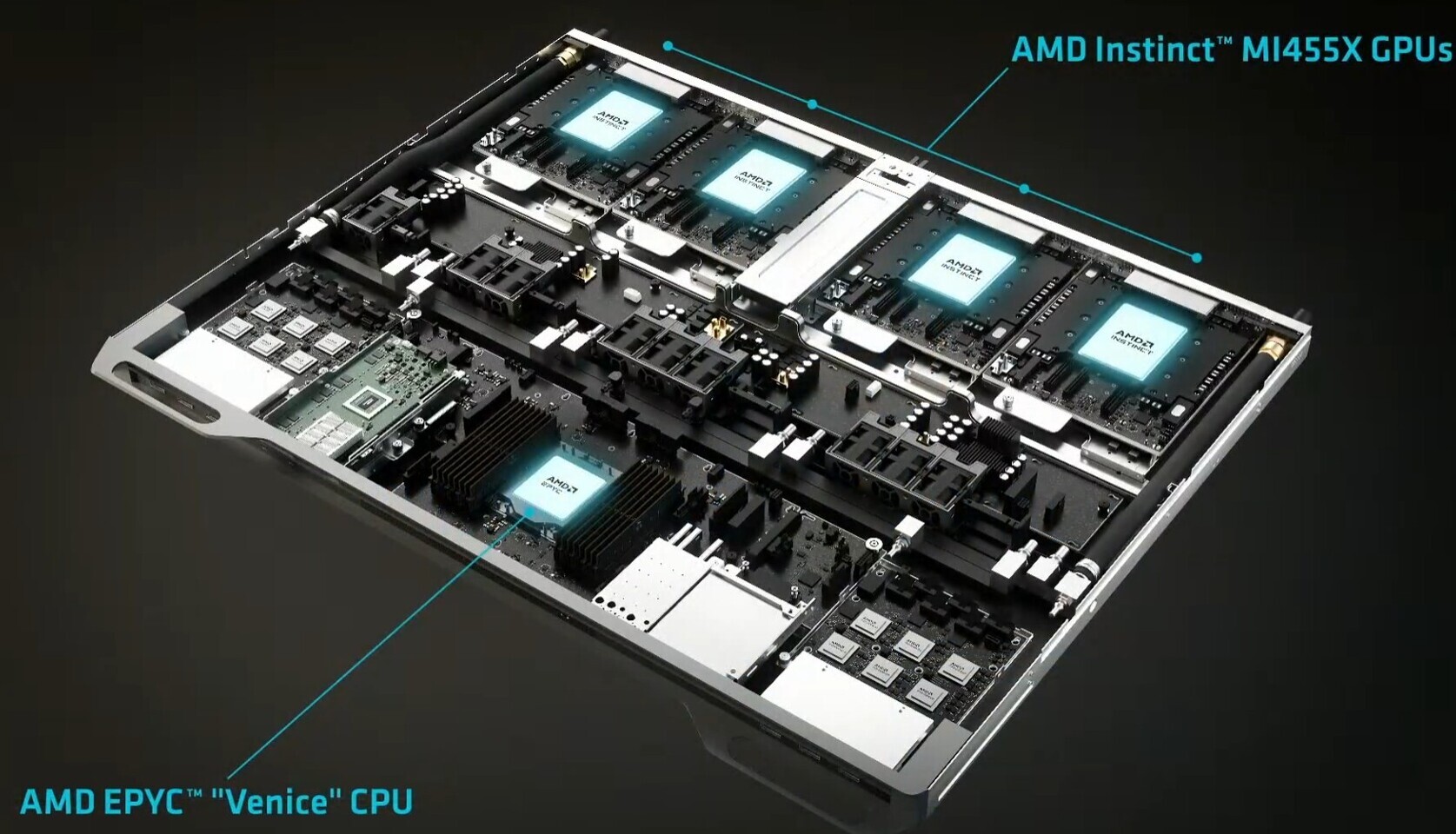

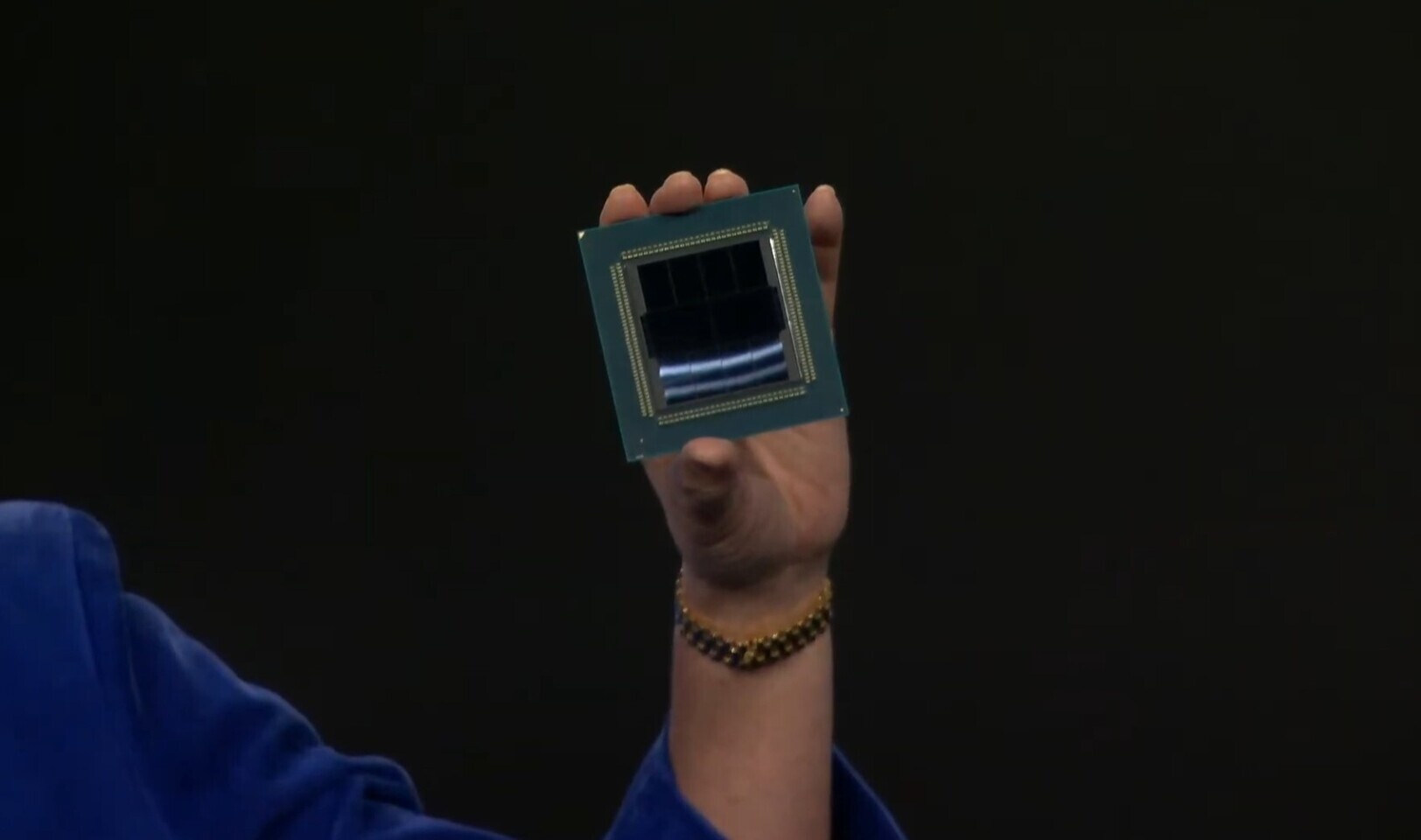

AMD CEO 리사 수 박사는 회사의 2026 국제 CES 행사에서 AMD MI455X AI GPU로 구동되는 2026년형 "Helios" AI 랙을 이끄는 차세대 EPYC "Venice" 엔터프라이즈 프로세서를 들어 보였습니다. 랙의 각 노드는 4개의 MI455X GPU와 256코어/512스레드 구성을 갖춘 1개의 EPYC "Venice" 프로세서를 특징으로 합니다. 이 패키지는 현재의 EPYC 칩과 비교하여 상당히 다른 칩렛 레이아웃을 특징으로 합니다. 이는 4nm 공정으로 제작된 두 개의 얇은 중앙 서버 I/O 다이(sIOD)를 보여주며, 그 양옆에는 각각 2nm 파운드리 공정으로 제작되고 32개의 "Zen 6" 코어를 탑재한 CCD가 최대 8개 배치되어 있습니다.

현시점에서 우리는 이것들이 높은 클럭 속도를 지속할 수 있는 풀 사이즈 "Zen 6" 코어인지, 아니면 동일한 ISA와 IPC를 특징으로 하지만 최대 클럭 속도가 더 낮은 압축된 "Zen 6c" 코어인지는 알 수 없습니다. 각 "Venice" 패키지는 16채널 DDR5 메모리 인터페이스(32 서브 채널)를 특징으로 하며, 이는 AMD가 왜 sIOD를 고속 스위칭 패브릭을 사용하여 측면으로 결합된 두 개의 칩으로 분리해야 했는지를 설명해 줍니다. 또한 AMD는 4개의 AI GPU, DPU 및 800G NIC를 지원하기 위해 현세대 대비 "Venice"의 PCIe 및 CXL 레인 수를 크게 늘릴 것으로 예상됩니다.

--------------------------------------------------------------------------------------광고(Advertising)--------------------------------------------------------------------------------------------------------

ASUS, NUC 16 Pro "Intel P...

ASUS, NUC 16 Pro "Intel P...

AMD Ryzen AI Halo: 미니 PC 그 ...

AMD Ryzen AI Halo: 미니 PC 그 ...